MIPS-architektúra

A MIPS (az angol Microprocessor without Interlocked Pipeline Stages rövidítése) egy 32/64 bites RISC utasításkészlet-architektúra (angolul: instruction set architecture, ISA), amelyet a MIPS Computer Systems (jelenleg MIPS Technologies) cég fejlesztett ki az 1980-as évek elején.[1] Eredetileg a MIPS-architektúra 32 bites volt, a 64 bites felépítés későbbi fejlesztés eredménye. A MIPS utasításkészletnek több változata létezik, ezek a következők: MIPS I, MIPS II, MIPS III, MIPS IV, MIPS V, MIPS32, és MIPS64. Jelenleg a MIPS32 és MIPS64 revíziókat használják a 32 és 64 bites rendszerekhez, ezek a regiszterkészletet is meghatározzák az utasításkészlet mellett.

Több opcionális kiterjesztése van, így a MIPS-3D ami egy egyszerű lebegőpontos SIMD utasításkészlet általános 3D feladatokhoz,[2] az MDMX (MaDMaX) – ez egy jóval átfogóbb egész típusú (integer) SIMD utasításkészlet, amely a 64 bites lebegőpontos regisztereket használja, a MIPS16e, amely tömörítést ad az utasításfolyamhoz, így a programok kisebb helyet foglalnak,[3] valamint a MIPS MT, amely többszálú utasításvégrehajtást (multithreading) ad a készlethez.[4]

A MIPS-architektúra a legtöbb számítógép-architektúra kurzuson tananyag. Nagy hatással volt a későbbi RISC felépítésű processzorokra, mint pl. a DEC Alpha-ra.

MIPS típusú processzorokat főleg a beágyazott rendszerekben használnak, így pl. Windows CE eszközökben, routerekben, házi használatú gateway-ekben, valamint játékkonzolokban, pl. Sony PlayStation 2 és PlayStation Portable gépekben. 2006-ig az SGI cég MIPS processzorokkal szerelt számítógépeket és munkaállomásokat forgalmazott (pl. SGI Indigo). MIPS implementációkat több cég is alkalmazott a termékeiben: ilyenek a Digital Equipment Corporation (DEC), NEC, Pyramid Technology, Siemens Nixdorf, Tandem Computers és mások az 1980-as évek végén és az 1990-es években. Az 1990-es évek második felében a RISC processzorok egyharmada MIPS változat volt.

2021 márciusában a MIPS vállalat bejelentette, hogy a MIPS-architektúra fejlesztése befejeződött, és a vállalat átáll a RISC-V architektúrájú processzorok fejlesztésére.[5]

Történet szerkesztés

A kezdetek szerkesztés

1981-ben a Stanford Egyetemen John L. Hennessy és csapata kezdte el a munkát, ami a MIPS processzor kifejlesztéséhez vezetett. A kiinduló elgondolás a következő volt: hogyan lehetne növelni a processzorok teljesítményét mélyebb / több fokozatú utasítás-futószalag (pipeline) használatával. A futószalagos technika már ismert volt ebben az időben, pl. az IBM 801-es kísérleti gépben már alkalmazták, de még nem fejlődött ki teljesen. A CPU-k néhány meghatározott alapegységből épülnek fel, ilyenek pl. az ALU (aritmetikai-logikai egység, az egész számokkal végzett műveletekhez), a memóriakezelést megvalósító betöltő/tároló (load/store) egység, stb. A hagyományos nem optimalizált felépítésben egy adott művelet (egy program utasítássorozatában) általában befejeződik, mielőtt a következő utasítás végrehajtása megkezdődne; a futószalagos architektúrában azonban az egymást követő utasítások végrehajtási fázisai átfedik egymást. Így például miközben a processzor egy utasítást hajt végre a lebegőpontos egységben, a betöltő/tároló egység beolvashatja a következő utasítást.

A futószalag használatának egyik fő akadálya az volt, hogy néhány utasítás, mint pl. az osztás, végrehajtása tovább tart, így a CPU-nak várnia kell, mielőtt a következő utasítás bekerülne a futószalagba. Az egyik megoldás erre a problémára az események közötti zárolások (interlock) használata volt, amely lehetővé tette a végrehajtási fokozatok számára a foglaltság jelzését és a sorban álló többi fázis várakoztatását. Hennessy csapata ezt a zárolást tekintette a teljesítményt korlátozó legfőbb akadálynak, mivel a zárak/reteszek a CPU összes egységével kommunikálnak, ami időbe telik, és a reteszelés az órajel növelését is korlátozza. A MIPS fő tervezési szempontja az volt, hogy minden egyes utasítás-fázis, a gyorsítótár-hozzáférést is beleértve, egy ciklus alatt végrehajtható legyen, megszüntetve az összefonódó zárolásokat és lehetővé téve az egyciklusos utasítás-végrehajtást.

Bár a tervezés során (a fentiekből kiindulva, ádáz vitákat követően) kihagytak néhány hasznos utasítást, mint pl. a szorzást és osztást, mégis érezhető volt, hogy egy ilyen rendszer összteljesítménye drámaian megnövekszik, mert lehetővé teszi magasabb órajelen működő chipek előállítását. A sebességnövekedést nehéz lett volna a központi zárolás megtartásával elérni, mivel a zárolás kezeléséhez szükséges idő éppen úgy függ az áramkör lapkaméretétől, mit az órajeltől.

A másik különbség a MIPS és a konkurens Berkeley RISC felépítés között a szubrutinhívások kezelése. A RISC architektúra ún. regiszterablakokat használ erre az igen gyakori feladatra, azonban ez korlátozza többszintű hívások esetén az elérhető hívási mélységet. Minden szubrutinhívásnál külön regiszterkészletre van szükség, ami növeli a processzor területigényét, ezzel együtt a kialakítás bonyolultságát is. Hennessy úgy gondolta, hogy egy 'figyelmes' fordítóprogram mindig talál szabad regisztereket, mielőtt hardveres megvalósításhoz kellene fordulni, és a regiszterek számának egyszerű növelése nemcsak hogy leegyszerűsíti ezt a feladatot, hanem még növeli is a teljesítményt.

Más tekintetben a MIPS egy tipikus RISC típusú konstrukció. Az utasításkódok lerövidítése érdekében a RISC kialakításokban csökkentették a kódolandó utasítások számát. A MIPS esetében a 32 bites utasításszóból 6 bitet foglal el az utasítás kódja (opkód), a maradék 26 bit tartalmazhat egy ugrási címet, vagy 4 db 5 bites mezőn 3 regisztercímet, egy eltolási értéket és az utasításkód másik 6 bitjét. Egy másik formátum – a sok egyéb közül – meghatározhat 2 regisztert és egy 16 bites értéket, stb. Ez az utasításkód-kialakítás lehetővé teszi, hogy a processzor egy órajelciklus alatt beolvassa a művelet kódját és a hozzá tartozó adatokat; ellentétben a korábbi, nem-RISC kialakítású processzorokkal: pl. a MOS Technology 6502 külön órajelciklusok alatt olvasta be az opkódot és az adatokat. Ez az egyik legjelentősebb teljesítménynövelő tényező a RISC kialakítások esetén. Újabban a nem-RISC kialakítású processzorok is képesek hasonló sebességet elérni, más módszerek használatával.

Az első hardware szerkesztés

1984-re Hennessy már belátta a tervezetben rejlő üzleti lehetőségeket és otthagyta a Stanfordot, hogy megalapítsa a MIPS Computer Systems céget. A vállalkozás első terméke, az R2000-es mikroprocesszor, 1985-ben jelent meg, majd később a továbbfejlesztett változat, az R3000-es 1988-ban. Ezeket elsősorban a Silicon Graphics (SGI) munkaállomás-sorozatában használták fel. A kereskedelemben megjelent processzorok kialakítása eltért a Stanfordon végzett kutatás eredményeitől, mivel ezekben volt szorzás és osztás utasítás, és a hardveres zárolások többségét is megvalósították. A tervezésben részt vett Earl Killian szoftvertervező is; ő a MIPS III 64 bites utasításkészlet kiterjesztés és az R4000-es mikroarchitektúra vezető tervezője.[6][7]

A MIPS 1991-ben hozta forgalomba első 64 bites processzorát, az R4000-et. Ez fejlettebb TLB-vel (translation lookaside buffer, asszociatív cache címfordításhoz) rendelkezett, amelyben a bejegyzés nem csak a virtuális címet, hanem a virtuális címmező azonosítót is tartalmazta, ennek a haszna a mikrokernelek teljesítményében jelentkezett,[8] a konkurens architektúráknál (Pentium, PowerPC, Alpha) ugyanis a gyakori kontextus-váltások során üríteni kell a TLB-t és ez lassulást okoz. A piaci megjelenéskor azonban a MIPS pénzügyi nehézségekbe ütközött. A kialakítás annyira fontos volt az SGI számára, ami ez idő tájt a MIPS egyik legjelentősebb ügyfele volt, hogy 1992-ben 333 millió dollárért megvásárolta a teljes céget, ezzel garantálva a kialakítás fennmaradását. Az SGI leányvállalataként a cég MIPS Technologies néven folytatta tevékenységét.

Licencelhető architektúra szerkesztés

1990 elején a MIPS elkezdte licencelni a fejlesztéseit külső cégeknek. Az ötlet sikeresnek bizonyult, ami főleg a mag egyszerűségének köszönhető, ui. ez sok olyan felhasználási területet is megnyitott az architektúra számára, ahol eddig kevésbé hatékony CISC megoldásokat használtak, hasonló kapuszám (gate count) és ár mellett. (A kapuszám és az ár szoros összefüggésben van, az ár arányban áll a kivezetések számával is.) A Sun Microsystems is megpróbálkozott a SPARC mag licencelésével, de ezzel közel sem volt annyira sikeres. Az 1990-es évek végére a MIPS a legerősebb helyet foglalta el a beágyazott rendszerek előállításának terén – 1997-ben a 48-milliós MIPS-alapú leszállított processzorral az elsődleges RISC CPU szállítóvá vált, amivel megelőzte a híres 68k processzorcsaládot. A MIPS annyira sikeres volt, hogy 1998-ban az SGI leválasztotta a céget (eladta a részvényeit), így a MIPS Technologies önálló vállalkozásként működött tovább. A MIPS bevételének fele ma is a fejlesztéseik licenceléséből származik, a többi bevétel nagy része fejlesztési szerződésekből, melyek alapján magokat fejlesztenek külső cégeknek.

1990-ben a MIPS végleges formába hozta licencelési rendszerét, ami két alapvető kialakításra épül: a 32 bites MIPS32 és a 64 bites MIPS64 architektúrákra. A MIPS32 a MIPS II utasításkészleten alapul néhány kiegészítéssel a MIPS III, MIPS IV és MIPS V-ből; a MIPS64 alapja a MIPS V. A NEC, Toshiba és SiByte (amit később megvásárolt a Broadcom[9]) a bejelentéskor megszerezték a MIPS64 licencét, később csatlakozott hozzájuk a Philips, LSI Logic és az IDT. A konstrukció sikeres volt, így mostanára a számítógép-szerű eszközök (kéziszámítógépek, set-top boxok, stb.) piacán a „nehézsúlyú” magok között a legelterjedtebb típus a MIPS.

A MIPS-architektúra licencelhetősége sok induló processzorgyártó cég érdeklődését fölkeltette. Az egyik ilyen volt a Quantum Effect Devices (QED). Az R4300i jelű processzort tervező csoport indította a SandCraft céget, ami a R5432-et tervezte a NEC számára, és később az SR71000 jelű modellt, ami az első soronkívüli végrehajtású (out-of-order execution) processzor volt a beágyazott eszközök piacán.

Az eredeti DEC StrongARM fejlesztőcsoport hirtelen két cégre bomlott: egyik a SiByte, ami a SB-1250 gyártója – ez volt az egyik első nagy teljesítményű MIPS-alapú SoC; míg az Alchemy Semiconductor (melyet később az AMD felvásárolt) a kis fogyasztású alkalmazásokhoz szánt Au-1000 SoC gyártója volt. A Lexra DSP kiterjesztéssel ellátott MIPS-alapú architektúrára épülő audio-chipekkel jelentkezett és többszálú programfuttatást támogató kiterjesztéssel a hálózati eszközök terén. Mivel a Lexra nem licencelte az architektúrát, két per is indult ellene. Az elsőt gyorsan lezárták, mikor a Lexra megígérte, hogy nem reklámozza MIPS-kompatibilis jelzővel a termékeit. A második, ami a MIPS 4814976 sz., a nemkiegyenlített memória-hozzáférés kezelését érintő szabadalmát érintette, hosszan elhúzódott, végül azzal ért véget, hogy a Lexra ingyenes licencet és egy nagyobb összeget kapott a MIPS Technologies-től.

Két további cég is megjelent a piacon, amik a többmagos MIPS-architektúrájú processzorok készítésére specializálódtak. A Raza Microelectronics, Inc. megszerezte a sikertelen SandCraft termékvonalának jogait és később nyolcmagos rendszerekkel állt elő, amelyek a telekommunikációs és hálózati piacot célozták meg. A Cavium Networks, ami eredetileg biztonsági processzor szállító volt, eleinte nyolcmagos, később 32 magos processzorokat állított elő, ugyanarra a piacra. Mind a két vállalat házon belül fejlesztette ki az általuk gyártott processzormagokat, csak az architektúrát licencelte, kész MIPS CPU magok vásárlása helyett.

A desktop piac elvesztése szerkesztés

MIPS processzoros munkaállomásokat több cég is gyártott, pl. a SGI, MIPS Computer Systems, Inc.,[10] Whitechapel Workstations, Olivetti, Siemens-Nixdorf, Acer, Digital Equipment Corporation, NEC és DeskStation.

Az architektúrát a következő operációs rendszerek támogatták: az SGI IRIX operációs rendszere, Microsoft Windows NT (a 4.0 verziótól kezdve a támogatás megszűnt), Windows CE, Linux, BSD, UNIX System V, SINIX, QNX, valamint a MIPS Computer Systems saját RISC/os operációs rendszere.

A 90-es évek elején valószínűnek tűnt, hogy a MIPS és a többi nagy teljesítményű RISC processzoros rendszer lekörözik az Intel IA32 architektúrát. A feltételezést erősítette az a tény, hogy a Microsoft Windows NT első két verziója támogatta a Alpha, MIPS és PowerPC processzorokat is - és kisebb mértékben (működő bemutató szintjén) a Clipper és a SPARC architektúrákat is. Azonban az Intel gyorsan reagált és kibocsátotta a gyorsabb Pentium processzorsorozatát, és a Microsoft Windows NT v4.0 pedig az Intel és Alpha processzorokon kívül minden egyéb processzor támogatását megszüntette. Az SGI Itanium és IA32 architektúrákra való áttérése után[11] a MIPS processzorok használata az asztali gépekben szinte teljesen megszűnt.

Beágyazott eszközök szerkesztés

Az 1990-es évek során a MIPS-architektúra széles körben elfogadottá vált a beágyazott eszközök piacán, ezen belül főleg a számítógépes hálózati eszközök, telekommunikáció, videójátékok és videójáték-konzolok, nyomtatók, digitális televíziók és set-top boxok, DSL és kábel-modemek, valamint PDA-kban való felhasználás terén. A beágyazott MIPS eszközök alacsony energiafelvétele és hőkibocsátása, a fejlesztői eszközök és a felépítés sajátosságainak széles körű elérhetősége miatt a MIPS processzorok felhasználása ezen a téren valószínűleg továbbra is jelentős marad.

Összerakható magok a beágyazott eszközök számára szerkesztés

Az elmúlt néhány évben a különböző MIPS generációkban használt technológia nagy részét a cég IP-magokként (semiconductor intellectual property core) is elérhetővé tette; ezeket szerkezeti elemekként lehet használni újabb beágyazottprocesszor-kialakításokban. A kínálat részei a 4K és 5K néven ismert alap 32 bites és 64 bites magok is. Ezeket építőkockákként lehet használni olyan kiegészítőkkel együtt, mint lebegőpontos egységek, SIMD rendszerek, ki- és bemeneti egységek széles választéka, stb.

A MIPS magok üzletileg sikeresek voltak, jelenleg fogyasztói és ipari termékekben alkalmazzák őket. MIPS magok találhatók az újabb Cisco, Linksys routerekben és a Mikrotik RouterBOARD eszközeiben, kábelmodemekben és ADSL modemekben, smartkártyákban,[12] lézernyomtatók központi egységeiben, set-top boxokban, robotokban, kéziszámítógépekben, a Sony PlayStation 2 és PSP játékkonzolokban. A mobiltelefon és PDA felhasználás terén a MIPS nem tudta kiszorítani a mindenütt jelenlévő rivális ARM architektúrát.

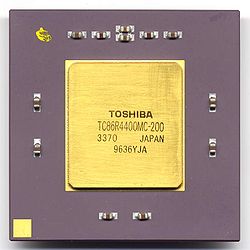

MIPS-architecturájú processzorok: IDT RC32438; ATI Xilleon; Alchemy Au1000, 1100, 1200; Broadcom Sentry5; RMI XLR7xx, Cavium Octeon CN30xx, CN31xx, CN36xx, CN38xx and CN5xxx; Infineon Technologies EasyPort, Amazon, Danube, ADM5120, WildPass, INCA-IP, INCA-IP2; Microchip Technology PIC32; NEC EMMA and EMMA2, NEC VR4181A, VR4121, VR4122, VR4181A, VR5432, VR5500; Oak Technologies Generation; PMC-Sierra RM11200; QuickLogic QuickMIPS ESP; Toshiba Donau, Toshiba TMPR492x, TX4925, TX9956, TX7901.

MIPS-alapú szuperszámítógépek szerkesztés

A MIPS-architektúra egyik jelentős alkalmazási területe a nagyon sok processzort tartalmazó szuperszámítógépekben való felhasználás.

A ’90-es években a SGI az asztali munkaállomásokról átváltott a nagy teljesítményű számítástechnikai piacra. Ezen a területen első ilyen termékcsaládja a Challenge sorozat volt; ez R4000 és R8000, majd később R10000 processzorokon alapult. A termékvonal sikeres volt, az 1990-es évek elejétől közepéig terjedő időszakban forgalmazták. (Ezeket a gépeket mostanában a server és multiprocesszoros server kategóriába sorolják[13]).

Az integrált R10000 megjelenése után a cég új rendszerrel jelentkezett, ez volt az Origin 2000, amely akár 1024 processzorig volt skálázható a NUMAlink cc-NUMA összekapcsolási technológiával. Az Origin 2000-et követte az Origin 3000 sorozat, ami szintén max. 1024 processzort tartalmazhatott, azonban ezek már R14000 és R16000 modellek voltak, amelyek órajele a 700 MHz-t is elérhette.

A SGI stratégiai döntés alapján beszüntette a MIPS-alapú szuperszámítógépek gyártását, mikor átállt az Intel IA-64 architektúra használatára.

2007-ben lépett a piacra az újonnan alakult SiCortex cég, amely szintén a nagy teljesítményű számítástechnikára specializálódott. A cég egy masszívan paralel rendszerű MIPS-alapú szuperszámítógéppel jelentkezett. Ezek a gépek a MIPS64 architektúrán alapultak és nagy teljesítményű, Kautz-gráf topológiájú összekapcsolási rendszert használtak. A rendszer igen energiatakarékos és nagy számítási teljesítménnyel rendelkezik; leginkább egyedi vonása, hogy többmagos feldolgozási csomópontokból épül fel (node). Egy node 6 db MIPS64 magot tartalmaz, egy crossbar memóriakontrollert, egy interconnect DMA engine-t, Gigabit Ethernet és PCI Express kontrollereket, mindezt egyetlen chipben. A chip fogyasztása 10 watt, teljesítménye 6 GFLOP. A legerősebb SC5832 jelű konfiguráció, egy egyszekrényes szuperszámítógép, 972 ilyen csomópontot, azaz 5832 MIPS64 processzormagot tartalmaz, amivel 8,2 teraFLOPS csúcsteljesítményre képes.

Loongson szerkesztés

A Loongson (kínai: 龙芯, pinjin:lóngxīn, magyaros:lunghszin) egy MIPS-kompatibilis 32 és 64 bites mikroprocesszor-család, amelyet a Kínai Tudományos Akadémia Számítógépes Technológiai Intézetében (Institute of Computing Technology, ICT) fejlesztettek ki, kb. 2001-től kezdve.[14] Ez a processzorcsalád Godson néven is ismert.[15]

A Loongson processzorok belső mikroarchitektúrája független kínai fejlesztés; a jogi viták elkerülése miatt a korai implementációkból hiányzott négy, a MIPS Technologies által levédett utasítás.[16] 2009 júniusában az ICT megvásárolta a MIPS32 és MIPS64 architectúrák licenceit, így ez a kompatibilitási akadály elhárult.[15][17] A Loongson processzorok fejlesztése a BLX IC Design Corporation segítségével valósult meg, a gyártó és forgalmazó cég a ST Microelectronics.

2006-tól kezdve több gyártó is piacra dobott Loongson-alapú számítógépeket, többek között kis fogyasztású nettop (mini PC) és laptop gépeket is.[18][19][20]

Dawning 6000 szerkesztés

A nagy teljesítményű Dawning 6000 kínai szuperszámítógép, amelynek tervezett sebessége meghaladja az egy billiárd műveletet másodpercenként (1 petaflops), szintén Loongson processzorokra épül: a gép kb. 10 000 Loongson processzort fog tartalmazni. A Dawning 6000-et jelenleg közösen fejleszti a Kínai Tudományos Akadémia Számítógépes Technológiai Intézete (ICT) és a Dawning Information Industry Company és becslések szerint a gép már 2011 végére elkészülhet. Ez lesz Kína első teljes egészében hazai alkatrészekből felépülő szuperszámítógépe.

ISA szintek szerkesztés

A MIPS processzorok pályafutása alatt az utasításkészlet-architektúra – ISA – többször is változott. Egy ISA definíció magában foglalja a natív adattípusokat, utasításkészletet, regisztereket, címzési módokat, memóriamodellt, megszakítás-, kivétel- és ki-/bemenetkezelést; a MIPS esetében ezeket ISA revízióknak vagy szinteknek nevezik. A hivatalosan bevezetett revíziók a MIPS I, MIPS II, MIPS III, MIPS IV és a MIPS V[21] voltak. Ezek közös tulajdonsága, hogy mindegyik magában foglalja az előző szinteket, azokkal teljesen kompatibilis és tartalmazza az addig bevezetett összes bővítményt és kiterjesztést. 1998-ban, mikor a MIPS kivált a SGI-ből, a cég inkább a beágyazott eszközök piacára fókuszált. Ekkoriban a teljes kompatibilitás kezdett problémát okozni, ezért az architektúrákat átdefiniálták; így jött létre a 32 bites MIPS32 és a 64 bites architektúrát leíró MIPS64 jelű revízió. A használatban gyakran a MIPS32 és MIPS64 meghatározás alatt csak valamilyen általános 32 bites vagy 64 bites MIPS processzort értenek.

A revíziók ill. szintek a következők:

SU MIPS szerkesztés

A Stanford Egyetemen az eredeti kutatási projekt eredményeképpen létrejött processzortervezet utasításkészlete. Ez nem volt hivatalos revízió és a későbbi szintek kompatibilitási tulajdonsága sem érvényes rá teljesen, de az összes későbbi ISA „ősének” tekinthető.

Az utasításkészletben nincs szorzás és osztás művelet; ezek helyett csak azok részműveleteit végző utasítások vannak. A szorzás és osztás elvégzését 3 speciális regiszter segíti, a Hi, Lo és Db. A műveletekhez a Booth algoritmus használható,[22] az erre implementált 4 utasítás segítségével: msetup, mstep, umend és dstep. Ezekkel az utasításokkal szoftveresen végrehajtható a (32 bites) egész típusú előjeles szorzás és osztás.[23] Hasonló utasítások felbukkannak pl. a MIPS-X és más RISC processzor-architektúrákban is (pl. az ETRAX CRIS architektúrában):

- mstart – multiply startup (szorzás kezdőlépés)

- mstep – multiply step (szorzás lépés)

- dstep – divide step (osztás lépés)

MIPS I szerkesztés

Ez egy 32 bites utasításokat tartalmazó alap MIPS utasításkészlet, amit az eredeti R2000 és R3000 processzorok implementálnak. Az I-es számot csak visszamenőlegesen, a többi revízió megjelenése után kapta.

MIPS II szerkesztés

A MIPS II első implementációja az R6000-es chipkészlet volt, amelyet 1988-ban kezdtek fejleszteni és 1989-ben mutattak be. A szerverekhez tervezett R6000-et a Bipolar Integrated Technology (BIT) gyártotta és értékesítette, de a processzor üzleti téren kudarcot vallott.

A MIPS I-hez képest csak néhány kisebb változtatás került bele. Ebben jelentek meg az újabb ll (load-linked), sc (store-conditional) – ezek a multiprocesszoros szinkronizációt szolgálják – és a branch likely utasítások (pl. beql, bnel stb.), amelyek a várakozási résben levő utasítást csak akkor hajtják végre, ha az ugrásra sor kerül. A lebegőpontos utasításkészletet kibővítették 64 bites betöltő és tároló utasításokkal, ami a MIPS I-hez képest gyorsította a duplapontosságú lebegőpontos számításokat. Ez a MIPS32 közvetlen elődje.[24]

MIPS III szerkesztés

A MIPS III 1991-ben jelent meg az R4000-es processzorcsaláddal együtt. Ez egy teljesen 64 bites architektúra, ebben jelennek meg a 64 bites regiszterek és (ALU) utasítások, 64 bites lebegőpontos koprocesszor, 64 bites virtuális címmező és 64 bites rendszerbusz. A FPU négyzetgyök műveletet kapott. Az R4000 processzor képes 32 bites üzemmódban is működni, ekkor a regiszterek 32 bitesek, egyébként 32 db 64 bites regiszter használható. Az utasítások továbbra is 32 bitesek. A processzorba beépült a MMU, az elsődleges gyorsítótár (cache) és a lebegőpontos koprocessszor (FPU). A processzorok ún. superpipeline futószalagot használnak.[25]

MIPS IV szerkesztés

A MIPS IV az architektúra negyedik változata. Magában foglalja a teljes MIPS III szintet és kompatibilis a MIPS utasításkészlet-architektúra összes megelőző szintjével. Elsőként az 1994-ben megjelent R8000 processzorban került alkalmazásra. A MIPS IV bővítményei:

- Regiszter + regiszter címzés a lebegőpontos betöltő és kiíró utasításokhoz

- egyszeres és dupla pontosságú lebegőpontos összeolvasztott (fused) szorzás-összeadás és szorzás-kivonás utasítások

- feltételes mozgató utasítások, egész és lebegőpontos értékekre

- lebegőpontos inverz négyzetgyök utasítás

- újabb feltételbitek a lebegőpontos vezérlő és állapotregiszterben, ezek száma így összesen 8-ra emelkedett.

MIPS V szerkesztés

Az architektúra ötödik verziója volt a MIPS V, amelyet 1996. október 21-én jelentették be az 1996-os Microprocessor Forumon.[26] Az 1990-es évek közepén a MIPS Technologies a SGI leányvállalata volt, és a legtöbb nem-beágyazott MIPS processzort a SGI grafikai munkaállomásaiban használták fel. A bővítés célja az volt, hogy a MIPS-architektúra közvetlenül támogassa a digitális médiafeldolgozást.

Az ISA bővítése két részből áll. Az első csoport utasításai a 3D-s grafikai algoritmusokban használhatók. A második kiterjesztés, a MIPS Digital Media Extensions – innen a MDMX vagy MaDMaX elnevezés – alkalmazásspecifikus kiterjesztés (ASE) audio, video és egyéb (pl. faxmodemben történő) jelfeldolgozási feladatokat célzott meg. A MDMX utasítások egész típusú adatokon működnek.[27][28]

MIPS V-implementációk nem jöttek létre. 1997-ben az SGI bejelentette a „H1” avagy „Beast” és a „H2” vagy „Capitan” mikroprocesszorokat. A H1 lett volna az első MIPS V implementáció, a megjelentetését 1999-re tervezték. A „H1" és „H2" projekteket később összevonták, majd 1998-ban hirtelen leállították.

A MIPS V-ben egy új adattípus jelent meg, a páros-egyszeres pontosságú szám (pair-single, PS), ami 2 egyszeres pontosságú lebegőpontos számból állt, egy 64 bites lebegőpontos regiszterben tárolva. Az új adattípushoz megfelelő, SIMD üzemmódban működő lebegőpontos aritmetikai, összehasonlító és feltételes mozgató utasítások tartoznak. Újabb utasításokat vezettek be a PS adatok betöltéséhez, átrendezéséhez és konvertálására. Ez volt az első, meglévő erőforrásokat használó lebegőpontos SIMD architektúra.[28]

MIPS32 szerkesztés

A MIPS32 a MIPS64 32 bites részhalmaza: 32 bites regiszterek és műveletek vannak benne.

MIPS64 szerkesztés

Az 1999-ben megjelent MIPS64 a MIPS V-ön alapul, 64 bites architektúrát definiál.

CPU-család szerkesztés

Az első kereskedelmi MIPS modell az 1985-ben bejelentett R2000 volt. Az eredeti tervekhez képest ez a modell többciklusos szorzás és osztás utasításokat is tartalmazott, egy valamelyest független chip-egységben. Hozzáadott új utasítások szolgálnak az eredmény letöltésére a szorzó egységből a regiszterfájlba; ezek blokkoló (interlocked) utasítások.

Az R2000 támogatja mind a big-endian, mind a little-endian bájtsorrendet, amit az indításkor lehet beállítani. 32 db 32 bites általános célú regisztere van, de nincs benne állapotregiszter (a tervezők úgy vélték, hogy ez csökkenti a teljesítményt), amiben hasonlít az AMD 29000-re és a DEC Alpha processzorra. A többi regisztertől eltérően a programszámláló közvetlenül nem elérhető.

Az R2000 négy koprocesszort támogat, ezek közül az egyik egy a fő processzorba beépített kivételkezelő, megszakításkezelő és memóriavezérlő egység, míg a többi három más célokra használható. Az egyik ilyen felhasználás az opcionális R2010 lebegőpontos koprocesszor (FPU), amelynek szintén 32 db 32 bites regisztere van, amelyeket 64 bites duplapontosságú regiszterekké lehet kombinálni, így ezek 16 db 64 bites duplapontosságú regiszterként használhatók.

Az R2000-et az R3000 követte 1988-ban, amely 32 KB adat- és utasításgyorsítótárral bővült, ezt később 64 KB-ra növelték. Ehhez jött még a cache-koherencia támogatás, ami a multiprocesszoros felhasználást segíti. Bár voltak hibák az R3000 többprocesszoros támogatásában, mégis több sikeres többprocesszoros konstrukcióban szerepelt. Az R3000 is tartalmazott egy beépített MMU-t, ami a processzorok közös jellemzője volt ezidőtájt. Az R2000-hez hasonlóan, az R3000 is kiegészíthető egy R3010 FPU-val. Az R3000 volt az első sikeres MIPS termék a piacon, és végül több mint egymillió készült belőle. Az R3000 felturbózott változata volt a R3000A, ennek órajele elérhette a 40 MHz-et, teljesítménye 32 VUPs (VAX Unit of Performance) volt. A MIPS R3000A-kompatibilis R3051 33,8688 MHz-es órajelet használt, ez volt a Sony PlayStation processzora. Más cégek is terveztek R3000-en alapuló processzorokat, ilyenek voltak pl. a Performance Semiconductor R3400, és az IDT R3500 modelljei, mind a kettő integrált R3010 FPU-val rendelkező R3000A volt. A Toshiba R3900 modellje volt talán az első SoC a Windows CE rendszerű korai kézi számítógépek számára. Az űralkalmazások számára kialakított sugárzástűrő változat, a Synova Mongoose-V processzora, egy R3000 integrált R3010 FPU-val.[29]

Az 1991-ben megjelent R4000 sorozat teljes 64 bites architektúrává terjesztette ki a MIPS utasításkészletet, egychipes mikroprocesszorban integrálva a fő processzort és a FPU-t, és rendkívül magas belső órajelen működött (a bevezetéskor 100 MHz). A magas órajel miatt azonban a cache-ek mérete 8 KB-ra csökkent és a hozzáféréshez három órajelciklusra volt szükség. A magas üzemi frekvenciát mély futószalag (akkoriban: szuper-futószalag) technikával érték el, azaz a futószalag (pipeline) fázisainak növelésével. A továbbfejlesztett R4400 1993-ban jelent meg. Ebben egy nagyobb, 16 KB-os elsődleges cache kapott helyet, nagyrészt hibamentes volt a 64 bites működés, és nagyobb L2 cache támogatással rendelkezett.

A céget 1992-ben felvásárolta a SGI. A MIPS, mint a SGI MIPS Technologies Inc. vagy MTI néven működő részlege tervezte az olcsó R4200 processzort, ebből kiindulva jött létre a még olcsóbb R4300i. Ez utóbbi egyik származtatott változata, a NEC VR4300 volt a Nintendo 64 játékkonzol processzora.[30]

A Quantum Effect Devices (QED), egy korábbi MIPS alkalmazottak által alapított külön cég, tervezte az R4600 Orion, az R4700 Orion (mindkettőnek Orion volt a kódneve), az R4650 és R5000 processzorokat. Míg az R4000 megemelt órajellel és a cache kapacitás feláldozásával növelte a sebességet, a QED kialakításokban a nagyméretű és gyors cache-re helyezték a hangsúlyt (a cache elérés csak két ciklust vett igénybe), valamint a szilíciumterület hatékony kihasználására. R4600 és R4700 processzorokat használtak az SGI Indy munkaállomás olcsó változatában, valamint az első MIPS alapú Cisco routerekben, a 36x0 és a 7x00 router-sorozatban. Az R4650 processzort az eredeti WebTV set-top boxok használták (ma Microsoft TV). Az R5000 FPU rugalmasabb egyszeres pontosságú lebegőpontos ütemezéssel rendelkezett, mint az R4000, és ennek eredményeként, az R5000-alapú SGI Indy munkaállomások sokkal jobb grafikai teljesítményt nyújtottak, mint a hasonló órajelű R4400 Indy-k, azonos grafikus hardver használata mellett. Az SGI, a javulást hangsúlyozandó, új nevet is adott az R5000-et használó régi grafikus kártyának. A QED később megtervezte az RM7000 és RM9000 processzorcsaládot, amit a beágyazott eszközök piacára szánt, pl. hálózati eszközökbe és lézernyomtatókba. A QED-et 2000 augusztusában felvásárolta a PMC-Sierra félvezetőgyártó cég; ez a cég további beruházásokat végzett a MIPS-architektúra fejlesztése érdekében. Az RM7000 egy 256 KB kapacitású Level 2 gyorsítótárat tartalmazott és egy vezérlőt az opcionális harmadik szintű cache számára. A PMC-Sierra RM9xx0 családja egy SOC eszközcsalád, amely tartalmazza a northbridge perifériavezérlő elemeket, mint memóriavezérlő, PCI kontroller, gigabit ethernet kontroller és gyors IO portokat, pl. HyperTransport portot.

Az 1994-es R8000 volt az első szuperskalár MIPS kialakítás, amely ciklusonként két egész vagy lebegőpontos műveletet, valamint két memóriaműveletet tudott végrehajtani. A kialakítás hat chip-ből állt: egy egész-típusú egység (16 KB utasítás és 16 KB adat cache-vel kiegészítve), egy lebegőpontos egység, három teljesen egyedi másodlagos cache tag RAM (kettő a másodlagos gyorsítótár hozzáférések számára, egy a busz figyelésére) és egy cache vezérlő ASIC. A kialakítás része két teljesen futószalagos dupla pontosságú szorzó-összeadó egység, amelyek képesek egy 4 MB chipen kívüli másodlagos cache-ből érkező adatfolyamot kezelni (stream). Az 1990-es évek közepén R8000-es processzor hajtotta a SGI POWER Challenge gépeit, később pedig a POWER Indigo2 munkaállomásokban szerepelt. Bár az FPU teljesítménye elég jól megfelelt tudományos területek felhasználóinak, a korlátozott egészértékű teljesítmény és a magas ár lenyomta a legtöbb potenciális felhasználó érdeklődését, emiatt az R8000 csak egy évig volt a piacon és eközben is meglehetősen ritka maradt.

1995-ben jelent meg az R10000 processzor. Ez egy egychipes kialakítású processzor, gyorsabb órajellel fut, mint az R8000 és nagyobb, 32 KB-os elsődleges utasítás- és adatgyorsítótárral rendelkezik. Ez a processzor szintén szuperskaláris, de a legjelentősebb újítás benne a soronkívüli vagy nemszekvenciális (out-of-order) utasítás-végrehajtás. Az egyszerű memória-futószalag és egyszerűbb FPU ellenére a jelentősen megnövelt egészértékű teljesítmény, az alacsonyabb ár és az elődjénél kompaktabb kiszerelés népszerűvé tette az R10000-et a felhasználók körében.

A későbbi modellek már mind az R10000 magon alapultak. Az 1998-ban megjelent R12000-nél használt, kezdetben 0,25, majd 0,18 mikronos folyamat csökkentette a chip méretét és segítette a magasabb órajel elérését. A javított R14000 (2001) lehetővé tette a magasabb órajelen való működést és a chipen kívüli kiegészítő DDR SRAM cache használatát. A soron következő R16000 (2003) és R16000A (2004) típusok további órajel-növekedést és kisebb lapkaméretet értek el (R16000: 2003. január, 700 MHz; R16000A: 2004. február, 800 MHz, majd 900 MHz, később ennek exkluzív modelljei elérték az 1,0 GHz-es órajelet).

A MIPS család további tagjai között ott van a rendhagyó R6000 is, ami egy a Bipolar Integrated Technology által gyártott, emittercsatolt logikával (ECL) megvalósított, MIPS II utasításkészletet használó processzor. Ennél a TLB és cache felépítése különbözik a MIPS család többi tagjáétól. Az R6000 nem nyújtotta az elvárt teljesítménynövekedést, és bár alkalmazásra talált a Control Data gépekben, gyorsan eltűnt a fő processzorpiacról.

CPU adatok táblázata szerkesztés

| Modell | Órajel (MHz) | Év | Folyamat (µm) | Tranzisztorok (millió) | Lapkaméret (mm²) |

Lábszám | Teljesítmény (W) | Feszültség (V) | A. cache (KB) | U. cache (KB) | L2 Cache | L3 Cache |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| R2000 | 8–16,67 | 1985 | 2,0 | 0,11 | ? | ? | ? | ? | 32 | 64 | nincs | nincs |

| R3000 | 12–40 | 1988 | 1,2 | 0,11 | 66,12 | 145 | 4 | ? | 64 | 64 | 0-256 KB külső | nincs |

| R4000 | 100 | 1991 | 0,8 | 1,35 | 213 | 179 | 15 | 5 | 8 | 8 | 1 MB külső | nincs |

| R4400 | 100–250 | 1992 | 0,6 | 2,3 | 186 | 179 | 15 | 5 | 16 | 16 | 1-4 MB külső | nincs |

| R4600 | 100–133 | 1994 | 0,64 | 2,2 | 77 | 179 | 4,6 | 5 | 16 | 16 | 512 KB külső | nincs |

| R4650 | 133–180 | 1994 | 0,64 | 2,2? | 77? | 179 | 4,6? | 5 | 16 | 16 | 512 KB külső | nincs |

| R4700 | 100–200 | 1996 | 0,5 | 2,2? | ? | 179 | ? | ? | 16 | 16 | külső | nincs |

| R5000 | 150–200 | 1996 | 0,35 | 3,7 | 84 | 223 | 10 | 3,3 | 32 | 32 | 1 MB külső | nincs |

| R8000 | 75–90 | 1994 | 0,7 | 2,6 | 299 | 591+591 | 30 | 3,3 | 16 | 16 | 4 MB külső | nincs |

| R10000 | 150–250 | 1996 | 0,35, 0,25 | 6,7 | 299 | 599 | 30 | 3,3 | 32 | 32 | 512 KB–16 MB külső | nincs |

| R12000 | 270–400 | 1998 | 0,25, 0,18 | 6,9 | 204 | 600 | 20 | 4 | 32 | 32 | 512 KB–16 MB külső | nincs |

| RM7000 | 250–600 | 1998 | 0,25, 0,18, 0,13 | 18 | 91 | 304 | 10, 6, 3 | 3,3, 2,5, 1,5 | 16 | 16 | 256 KB belső | 1 MB külső |

| MIPS32 4K | 90-167 | 1999 | 0,18 | 1,4-2,5 | ||||||||

| MIPS64 5K | 1999 | |||||||||||

| MIPS64 20K | 2000 | |||||||||||

| R14000 | 500–600 | 2001 | 0,13 | 7,2 | 204 | 527 | 17 | ? | 32 | 32 | 512 KB–16 MB külső | nincs |

| R16000 | 700–1000 | 2002 | 0,11 | ? | ? | ? | 20 | ? | 32 | 32 | 512 KB–16 MB külső | nincs |

| MIPS32 24K | 400 (130 nm) 750 (65 nm) 1468 (40 nm) |

2003 | 40 nm - 130 nm | ? | 0,83 | ? | ? | ? | 64 | 64 | 4-16 MB külső | nincs |

| MIPS32 34K | 500 (90 nm) 1454 (40 nm) |

2006 | 90 nm 65 nm 40 nm |

|||||||||

| MIPS32 74K | 1080 | 2007 | 65 nm | |||||||||

| MIPS32 1004K | 1,1 GHz | 2008 | 65 nm | |||||||||

| MIPS32 1074K | 1,5 GHz | 2010 | 40 nm |

Felhasználási területek szerkesztés

Legfőképp audiovizuális gépekben használják, de manapság már szélesebben körben kezd elterjedni.

Eszközök:

- Broadcom MIPS rendszerek (pl. Linksys WRT54G router) és processzorok[31]

- Cisco routerek

- SGI, DEC, Siemens munkaállomások

- Pocket PC / Windows CE PDA-k, leginkább Casio, HP, IBM, NEC, Philips gyártmányok, főleg a ’90-es évekből[32]

- Játékkonzolok: a Nintendo 64 processzora egy R4300i MIPS változat

- Sony játékkonzolok: PlayStation: 32 bites MIPS R3000A változat, PlayStation 2 Emotion Engine: 128 bites MIPS R5900 változat, PlayStation Portable: MIPS R4000

- TiVo digitális videofelvevők

- MIPS-X egy katonai célokra tervezett MIPS klón a ’80-as évekből, melyben van egy úgynevezett HSC (halt and spontaneously combust) utasítás, mely elégeti a processzort.[33]

Humor szerkesztés

- A „MIPS-X utasításkészlet és programozói kézikönyv” leírja a hsc utasítás (halt and spontaneously combust, kb: „leállás és öngyulladás”) működését, aminek során külön felhívja a figyelmet arra a nem elhanyagolható részletre, hogy az utasítás végrehajtásakor, miközben a processzor megsemmisül, a Reg(31) regiszter tartalma, azaz a szubrutin visszatérési cím – elveszik![33] Ebből következik, hogy a processzor megsemmisülése után a program nem folytatható. A kézikönyv azt írja, hogy ez az utasítás csak a NSA számára készült processzorokban szerepel és a védelmi jogosultságok megsértése esetén hajtódik végre, de (az angol wikipédia-oldal szerint) ez az utasítás csak egy tréfa volt.

- A Super Mario 64 játékban MIPS egy nyúl neve, akit Mariónak el kell kapnia Őszibarack Hercegnő kastélyában. Ez a játék a Nintendo 64 játékkonzolon fut, aminek az alapja egy MIPS-architektúrájú processzor (NEC VR4300).[34]

- A MIPS processzorok sebességét a legkönnyebb megmondani: minden MIPS processzor sebessége annyi MIPS, ahány MHz az órajele.

Lásd még szerkesztés

- DLX, egy hasonló architektúra, tervezte John L. Hennessy (eredeti MIPS tervező), oktatási célokra

- MIPS-X, a MIPS következő változatának szánt architektúra

Források szerkesztés

- ↑ Chow, Paul. Foreword, The MIPS-X RISC microprocessor (Google books) (angol nyelven), Norwell, MA, USA: Kluwer Academic Publishers, xix. o. [1989]. ISBN 0792390458. Hozzáférés ideje: 2011. március 24. „The first Stanford MIPS project started ... in 1981. That project produced working silicon in 1983 and a prototype for running small programs in early 1984.”

- ↑ MIPS-3D ASE. MIPS Technologies. (Hozzáférés: 2009. május 27.)

- ↑ MIPS16e. MIPS Technologies. (Hozzáférés: 2009. május 27.)

- ↑ MIPS MT ASE. MIPS Technologies. [2012. november 24-i dátummal az eredetiből archiválva]. (Hozzáférés: 2009. május 27.)

- ↑ Turley, Jim: Wait, What? MIPS Becomes RISC-V. Electronic Engineering Journal , 2021. március 8. [2021. március 21-i dátummal az eredetiből archiválva]. (Hozzáférés: 2021. március 28.)

- ↑ „Earl Killian”, 'Paravirtual', 2010. november 26.. [2012. február 13-i dátummal az eredetiből archiválva] (Hozzáférés: 2010. november 26.)

- ↑ „S-1 Supercomputer Alumni: Earl Killian”, 'Clemson University', 2005. június 28. (Hozzáférés: 2010. november 26.) „Earl Killian's early work w... As MIPS's Director of Architecture, he designed the MIPS III 64-bit instruction-set extension, and led the work on the R4000 microarchitecture. He was a cofounder of QED, which created the R4600 and R5000 MIPS processors. Most recently he was chief architect at Tensilica working on configurable/extensible processors.”

- ↑ Jochen Liedtke(1995). On micro kernel construction. 15th Symposium on Operating Systems Principles, Copper Mountain Resort, Colorado.

- ↑ Broadcom acquires MIPS core provider SiByte Archiválva 2012. október 4-i dátummal a Wayback Machine-ben, EE Times, Loring Wirbel, 11/6/2000 11:51 AM EST

- ↑ http://gentiane.org/~miod/mips/magnum/ Archiválva 2011. május 14-i dátummal a Wayback Machine-ben - egy MIPS gyártmányú gép: MIPS RC 3230 - Magnum - fotókkal

- ↑ SGI announcing the end of MIPS. [2008. március 7-i dátummal az eredetiből archiválva]. (Hozzáférés: 2011. június 9.)

- ↑ MIPS moves into smart cards with Gemplus deal, MIPS kerül a Gemplus smartkártyákba, Margaret Quan, EE Times, 7/27/2000 2:16 PM EDT

- ↑ https://en.wikipedia.org/wiki/SGI_Challenge - The Challenge, ..., is a family of server computers and supercomputers ...

- ↑ http://english.ict.cas.cn/rh/rd/200908/t20090820_33350.html - The Center successfully built Loongson-1 in 2002, which was the first high-performance general-purpose processor in China.

- ↑ a b http://www.origo.hu/techbazis/szamitogep/20090424-godson-2g-iden-erkezik-az-olcso-kinai-processzor.html, origo, 2009

- ↑ http://www.mdronline.com/mpr/h/2006/0626/202602.html China's Microprocessor Dilemma

- ↑ http://www.mips.com/news-events/newsroom/release-archive-2009/6_15_09.dot Archiválva 2011. május 8-i dátummal a Wayback Machine-ben China’s Institute of Computing Technology Licenses Industry-Standard MIPS Architectures

- ↑ LinuxDevices article about the Municator. [2012. december 16-i dátummal az eredetiből archiválva].

- ↑ 'Yeelong Specs. [2012. december 10-i dátummal az eredetiből archiválva]. (LinuxDevices, Oct. 22, 2008)

- ↑ http://www.osnews.com/story/21530 - The Loongson-2 MIPS Lemote Yeeloong Netbook, by h3rman on Thu 21st May 2009

- ↑ Archivált másolat. [2012. október 21-i dátummal az eredetiből archiválva]. (Hozzáférés: 2014. szeptember 15.)

- ↑ a Booth algoritmus az angol wikipédián

- ↑ SU MIPS instruction set, Appendix II

- ↑ Dominic Sweetman: See MIPS Run, Chapter 1, page 10.

- ↑ MIPS R4000 Microprocessor User’s Manual, 1994 MIPS Technologies, Inc.

- ↑ Silicon Graphics Introduces Enhanced MIPS Architecture to Lead the Interactive Digital Revolution. Silicon Graphics, Inc., 1996. október 21. [2012. július 10-i dátummal az eredetiből archiválva]. (Hozzáférés: 2011. augusztus 29.)

- ↑ MIPS Extension for Digital Media with 3D, 1996, by MIPS Technologies, Inc.. [2014. július 16-i dátummal az eredetiből archiválva]. (Hozzáférés: 2011. augusztus 29.)

- ↑ a b Gwennap, Linley (18 November 1996). "Digital, MIPS Add Multimedia Extensions". Microprocessor Report. pp. 24–28.

- ↑ http://www.synova.com/proc/mg5.html Archiválva 2005. december 26-i dátummal a Wayback Machine-ben Synova, 'Mongoose-V MIPS R3000 Rad-Hard Processor'

- ↑ NEC Offers Two High Cost Performance 64-bit RISC Microprocessors

- ↑ http://www.broadcom.com/products/Cable/High-Definition-Audio-Video-Graphics-System-Processors/BCM7038 Archiválva 2011. május 23-i dátummal a Wayback Machine-ben pl. BCM7038: 300 MHz 64 bites MIPS® CPU

- ↑ http://people.freebsd.org/~imp/pdamips.html - MIPS-alapú PDA-k

- ↑ a b Chow, Paul: MIPS-X Instruction Set and Programmer's Manual. (angol nyelven) (pdf). Technical Report CSL-86-289 pp. 65. Computer Systems Laboratory, Stanford University, 1986. május 1. [2011. június 1-i dátummal az eredetiből archiválva]. (Hozzáférés: 2011. március 24.): a 65. oldalon található a hsc utasítás leírása.

- ↑ [1]

Egyéb források:

- Dominic Sweetman: See MIPS Run, második kiadás, 2007, (a Google könyvek oldalán), ISBN 978-0-12-088421-6

- Linux/MIPS, Instruction Set Architecture Archiválva 2011. augusztus 24-i dátummal a Wayback Machine-ben

- HUP Wiki Archiválva 2020. június 3-i dátummal a Wayback Machine-ben

- ELTE, RISC assembly speciális kollégium

További információk szerkesztés

- MIPS-architektúrák a MIPS Technologies webhelyén

Szimulátorok, emulátorok:

Hírek, érdekességek szerkesztés

- http://hirek.prim.hu/cikk/2011/06/05/a_mips_architekturaju_processzorok_visszaternek_a_szerverpiacra – Újabb MIPS szerverprocesszorok (2011. június 5.)